# **Analog Products Catalog**

**VOLUME II**

# Introduction

Volume II of Intersil's Analog Products Catalog contains devices most recently introduced and recommended for new designs. These products have not previously been published in any Intersil catalog.

Note that Volume II does not contain the entire Intersii Analog Production Line. For the complete line, refer to the Product Line Listing, page iii of this catalog.

Further information on older Intersil analog products can be found in the Analog Products Catalog, Volume I.

# **Functional Index to Volume II**

|    | Page                                                                                   |        |

|----|----------------------------------------------------------------------------------------|--------|

|    | TRODUCTION                                                                             |        |

| Fl | JNCTIONAL INDEXi                                                                       | i      |

| PI | RODUCT LINE LISTINGii                                                                  | i      |

|    | Analog Switchesii                                                                      | i      |

|    | Analog Switch Drivers                                                                  | 1      |

|    | Data Display/Conversion Products                                                       |        |

|    | FET Input Operational Amplifiers                                                       |        |

|    | High Impedance Operational Amplifiersv                                                 | i      |

|    | High Speed Operational Amplifiersv                                                     | i      |

|    | JAN-38510 Operational Amplifiersv                                                      | i      |

|    | Low Power Operational Amplifiers                                                       | !      |

|    | Special Function Circuits                                                              | i      |

|    | Timersvi                                                                               |        |

|    | Voltage Followersvi                                                                    |        |

|    | Voltage Regulatorsvi                                                                   | i      |

| n  | ATA SECTION                                                                            |        |

| יט | Analog Switches                                                                        |        |

|    | DG180 thru 191 High Speed JFET Switches with Driver59                                  | 4      |

|    | IH200 CMOS Analog Gate                                                                 | ś      |

|    |                                                                                        |        |

|    | Analog Switch Drivers                                                                  |        |

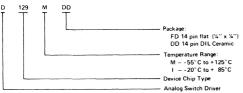

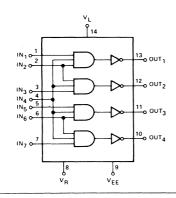

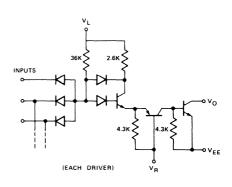

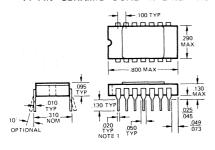

|    | D129 4-channel MOS FET Switch Driver with Decode                                       | ,      |

|    | Date Display/Conversion Products                                                       |        |

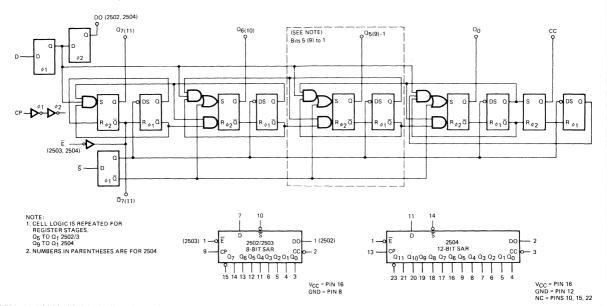

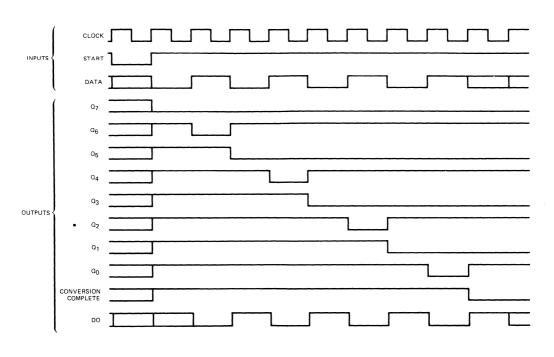

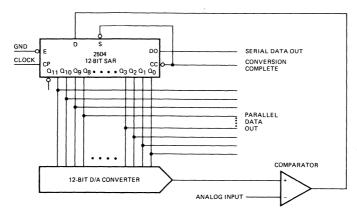

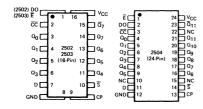

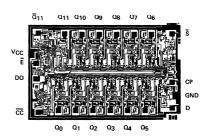

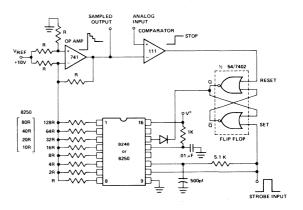

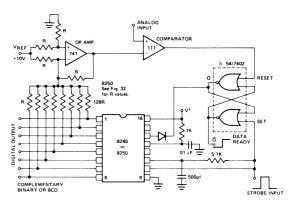

|    | 2504 Successive Approximation Register                                                 |        |

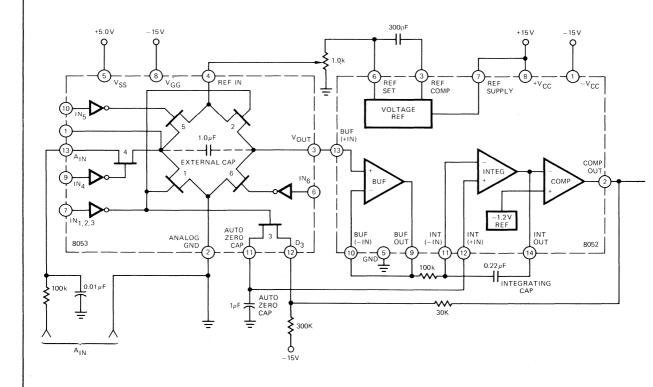

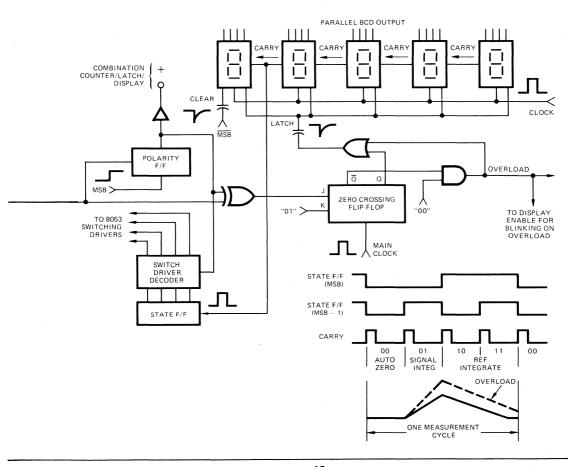

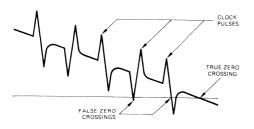

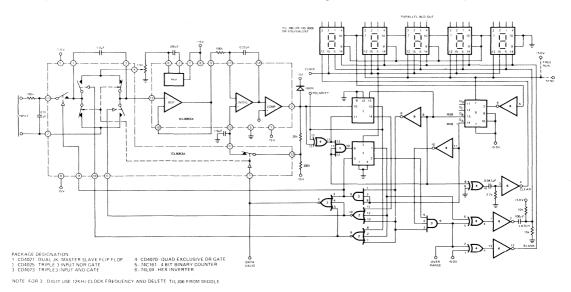

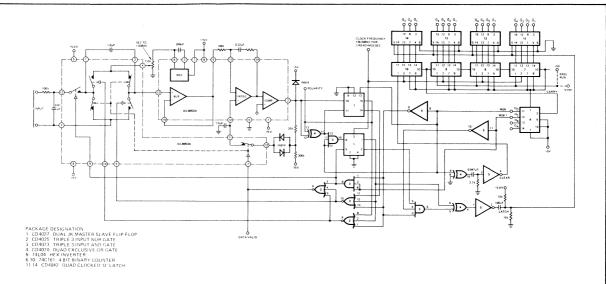

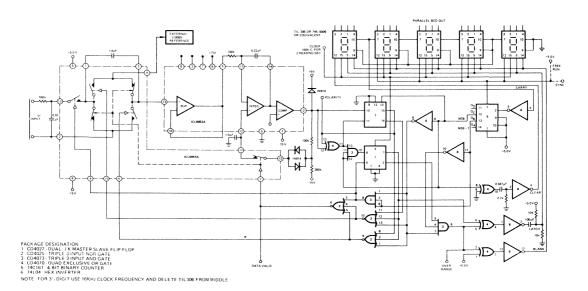

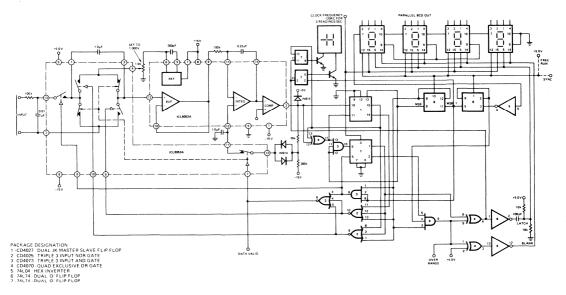

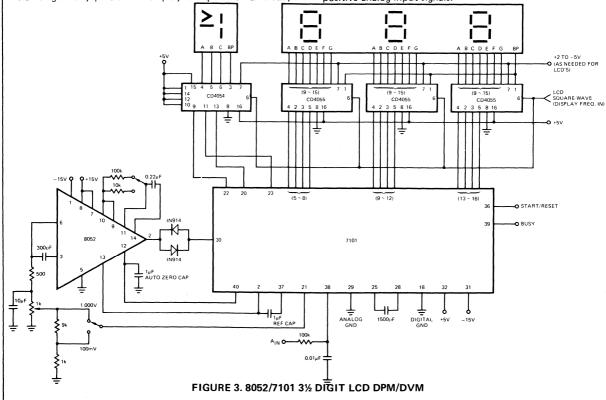

|    | 8052/7101 31/ <sub>2</sub> Digit A-D Pair                                              |        |

|    | 8052/7103 3½ Digit Pair For A-D Converters                                             |        |

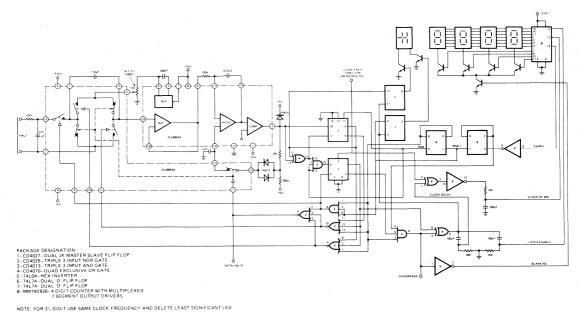

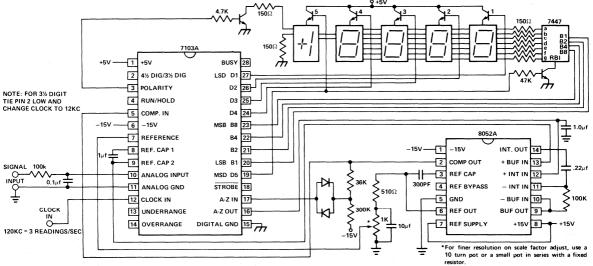

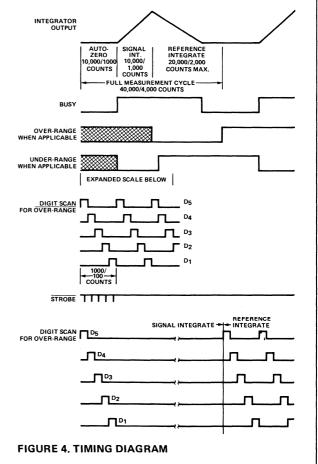

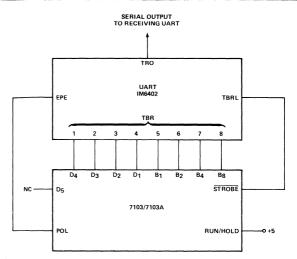

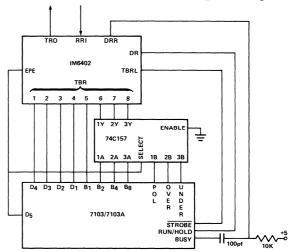

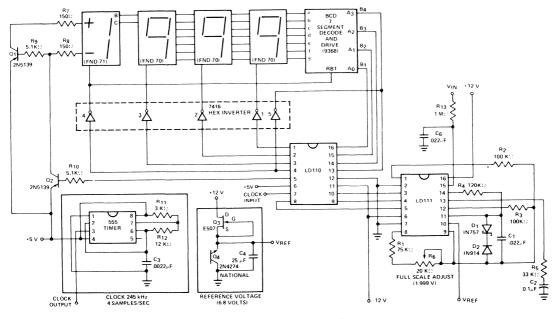

|    | 8052A/7103A 4½ Digit Pair For A-D Converters                                           |        |

|    | 8052/8053 3½ Digit Pair For A-D Converters                                             | :      |

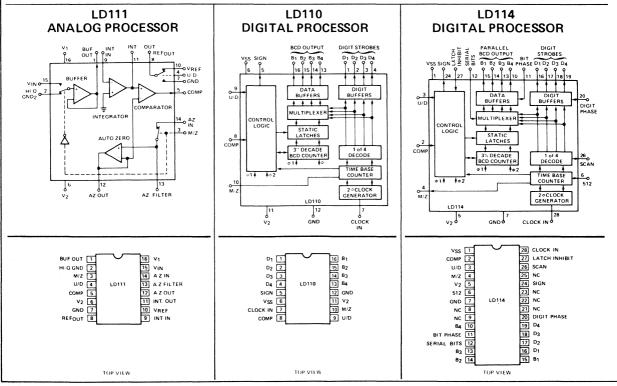

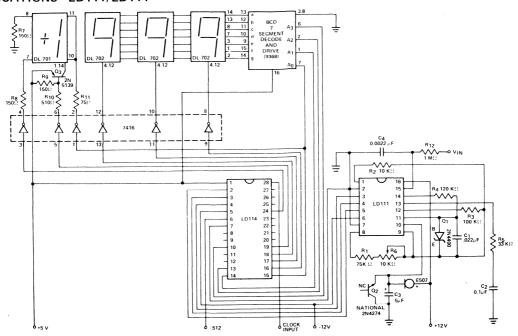

|    | LD110/LD111 3½ Digit A/D Converter Set                                                 | ,      |

|    | LD114 Multiple-Option Digital Processor                                                | ,      |

|    |                                                                                        |        |

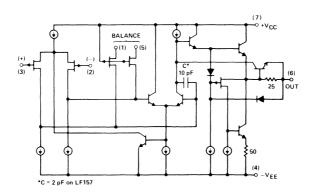

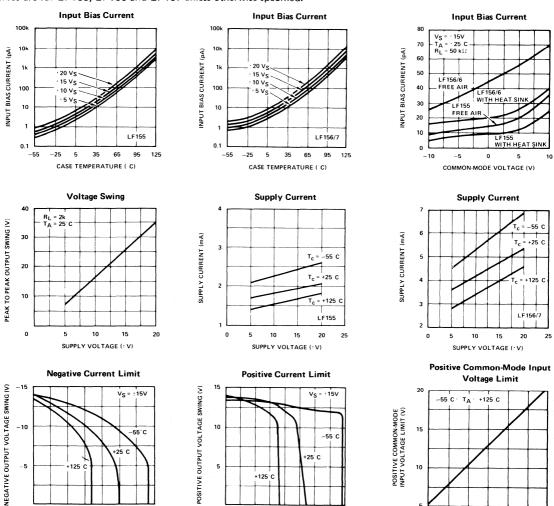

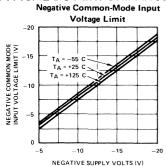

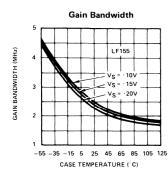

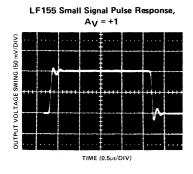

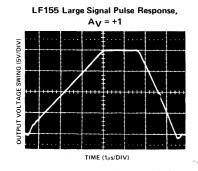

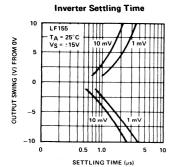

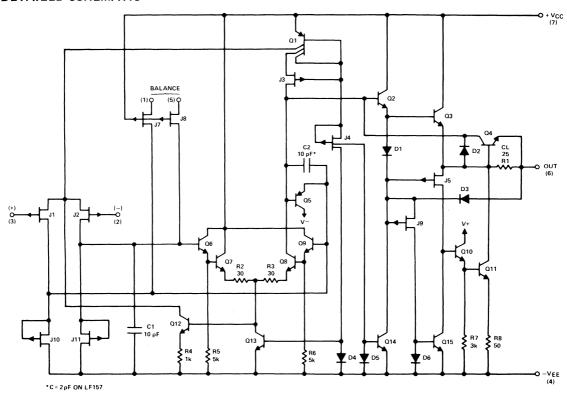

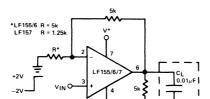

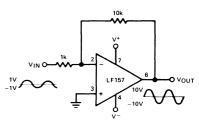

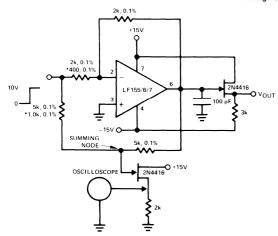

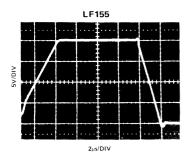

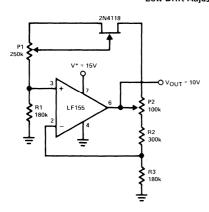

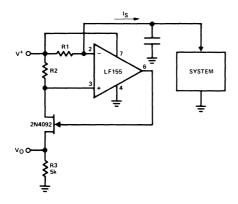

|    | FET Input Operational Amplifiers LF155/155A/255/355/355A Low Supply Current Op Amp93   | ,      |

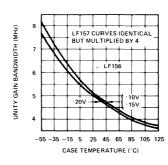

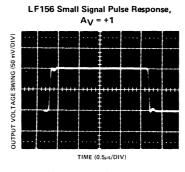

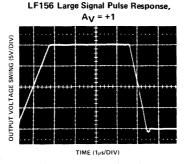

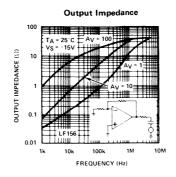

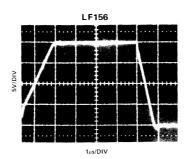

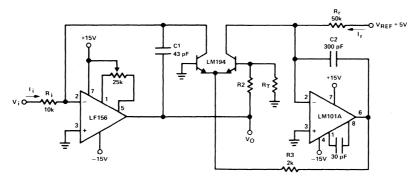

|    | LF156/156A/256/356A Wideband Op Amp                                                    | )<br>} |

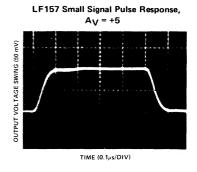

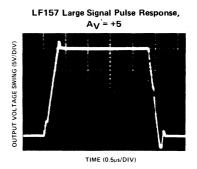

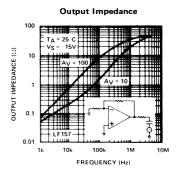

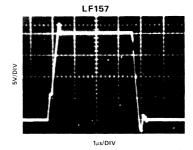

|    | LF157/157A/257/357A Wideband Uncompensated Op Amp                                      | 3      |

|    |                                                                                        |        |

|    | High Impedance Operational Amplifiers                                                  |        |

|    | 2600/2602/2605/2620/2622/2625 High Impedance Op Amp                                    |        |

|    | High Speed Operational Amplifiers                                                      |        |

|    | 2500/2502/2505/2520/2522/2525 High Slew Rate Op Amp                                    |        |

|    | 101 00700                                                                              |        |

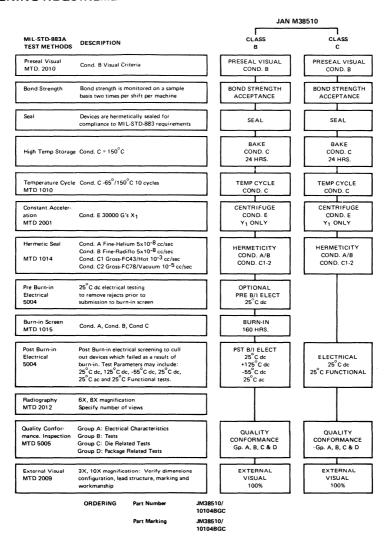

|    | JAN-38510 Products                                                                     |        |

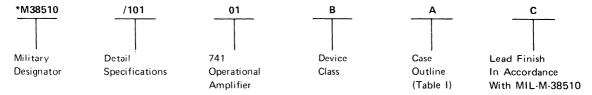

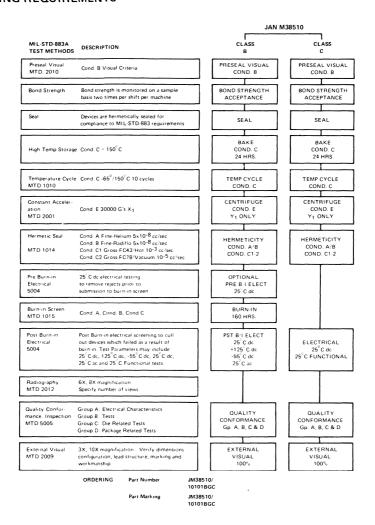

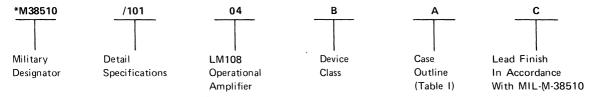

|    | JM38510/10101 MIL Spec 741 Op Amp                                                      |        |

|    | JM38510/10104 MIL Spec LM108 Op Amp                                                    |        |

|    |                                                                                        |        |

|    | Operational Amplifiers                                                                 |        |

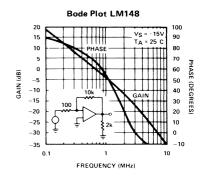

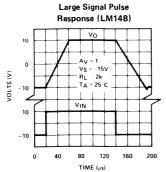

|    | LM148/248/348 Quad 741 Op Amp                                                          |        |

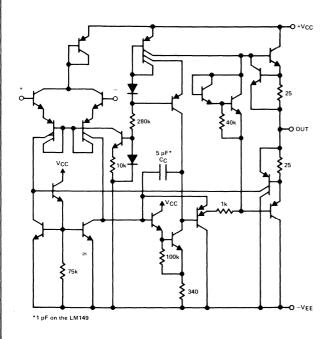

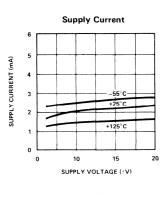

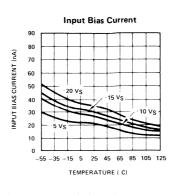

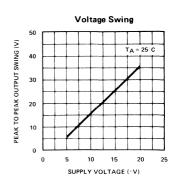

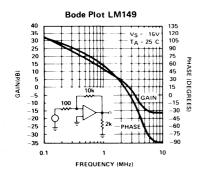

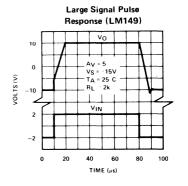

|    | LM149/249/349 Wideband Decompensated Op Amp109                                         | !      |

|    | Special Function Circuits                                                              |        |

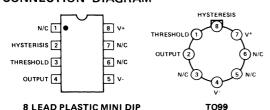

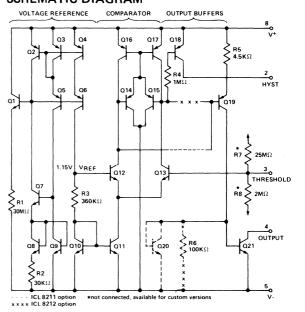

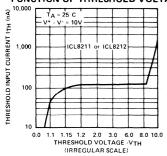

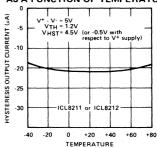

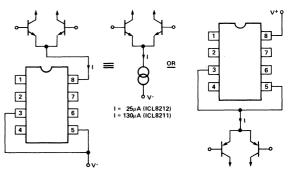

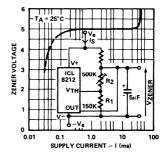

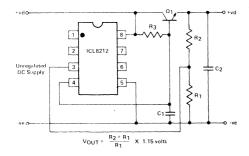

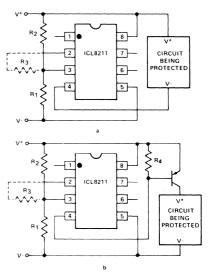

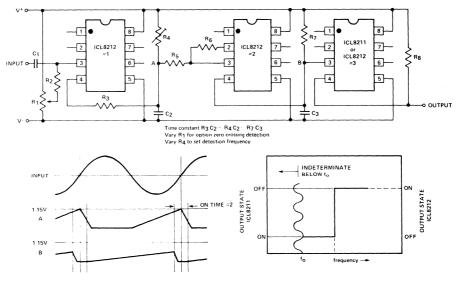

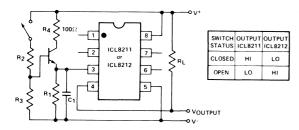

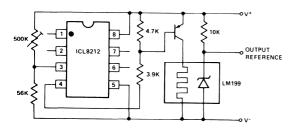

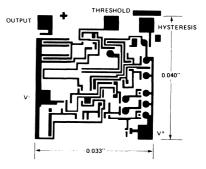

|    | 8211/8212 Micropower Voltage Detector/Indicator/Voltage Regulator/Programmable Zener63 | ;      |

|    |                                                                                        |        |

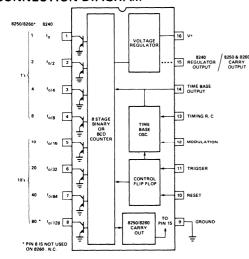

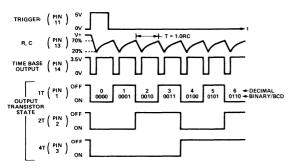

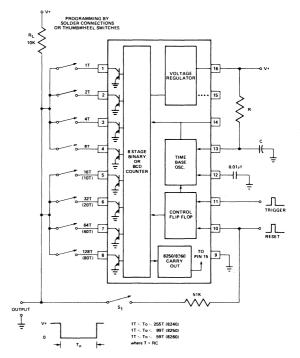

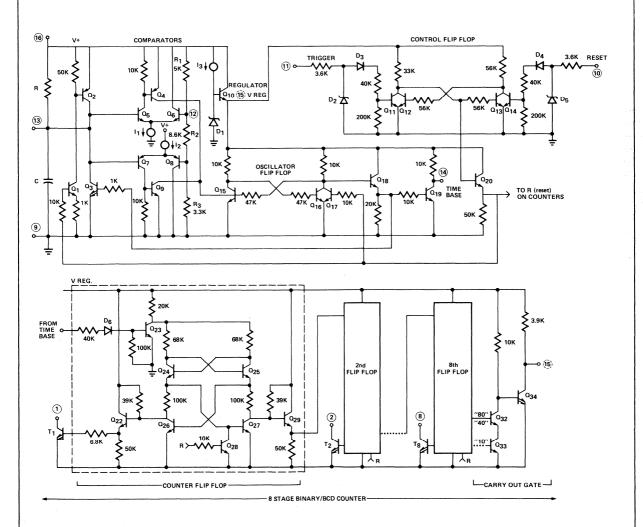

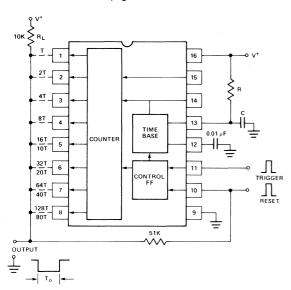

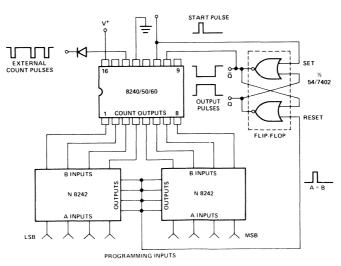

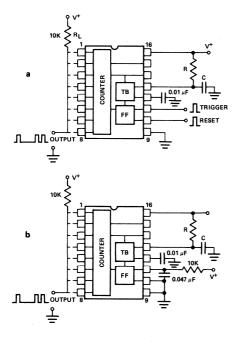

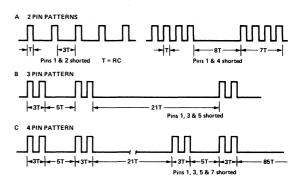

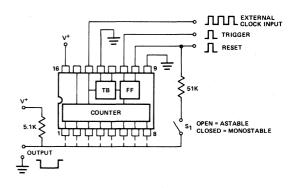

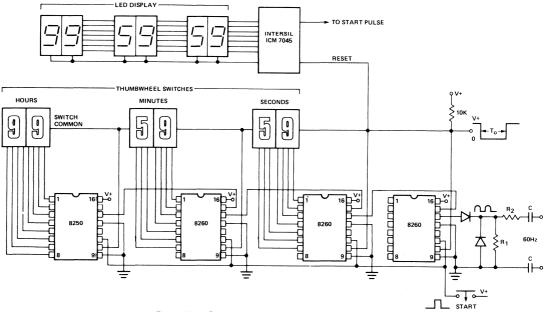

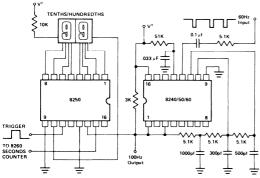

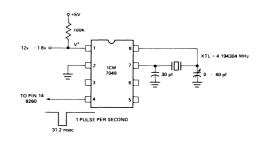

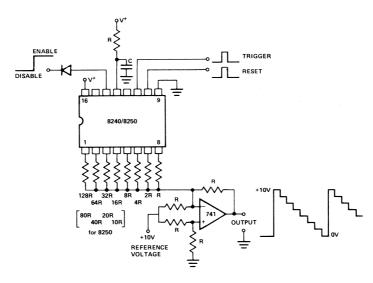

|    | <b>Timers</b><br>8240/8250/8260 Programmable Timer/Counter41                           |        |

|    | 02-40/0230/0250 Frogrammable Hiller/Counter                                            |        |

# **Product Line Listing**

A complete listing of the Intersil Analog Products line. Detailed specifications can be found in the Data Sections of Volumes I and II, as indicated here.

| Analog Switches                                                      | Vol. | Page     |

|----------------------------------------------------------------------|------|----------|

| DG111 2 Channel SPST MOS FET Switch with Driver                      | I    | 128      |

| DG112 2 Channel SPST MOS FET Switch with Driver                      | í    | 128      |

| DG116 4 Channel SPST MOS FET Switch with Driver                      | - 1  | 132      |

| DG118 4 Channel SPST MOS FET Switch with Driver                      | ı    | 132      |

| DG120 3 Channel Differential SPST MOS FET Switch with Driver         | - 1  | 136      |

| DG121 3 Channel Differential SPST MOS FET Switch with Driver         | 1    | 136      |

| DG123 5 Channel SPST PMOS Switch with Driver                         | 1    | 132      |

| DG125 5 Channel SPST PMOS Switch with Driver                         | - 1  | 132      |

| DG126/A 2 Channel Driver with DPST FET Switches                      | - 1  | 140      |

| DG129/A 2 Channel Driver with DPST FET Switches                      | 1    | 140      |

| DG133/A 2 Channel Driver with SPST FET Switches                      | j    | 140      |

| DG134/A 2 Channel Driver with SPST FET Switches                      | ı    | 140      |

| DG139/A Driver with N.O. and N.C. FET Switches                       | 1    | 144      |

| DG140/A 2 Channel Driver with DPST FET Switch                        | 1    | 140      |

| DG141/A 2 Channel Driver with SPST FET Switch                        | 1    | 140      |

| DG142/A Driver with N.O. and N.C. FET Switches                       | 1    | 144      |

| DG143/A Driver with N.O. and N.C. FET Switches                       | ı    | 144      |

| DG144/A Driver with N.O. and N.C. FET Switches                       | 1    | 144      |

| DG145/A Driver with N.O. and N.C. FET Switches                       | 1    | 144      |

| DG146/A Driver with N.O. and N.C. FET Switches                       | i    | 144      |

| DG151/A 2 Channel Driver with SPST FET Switches                      | i    | 140      |

| DG152/A 2 Channel Driver with SPST FET Switches                      | i    | 140      |

| DG153/A 2 Channel Driver with DPST FET Switches                      | i    | 140      |

| DG154/A 2 Channel Driver with DPST FET Switches                      | i    | 140      |

| DG161/A Driver with Differentially Driven N.O. and N.C. FET Switches | i    | 144      |

| DG162/A Driver with Differentially Driven N.O. and N.C. FET Switches | i    | 144      |

| DG163/A Driver with Differentially Driven N.O. and N.C. FET Switches | i    | 144      |

| DG164/A Driver with Differentially Driven N.O. and N.C. FET Switches | i    | 144      |

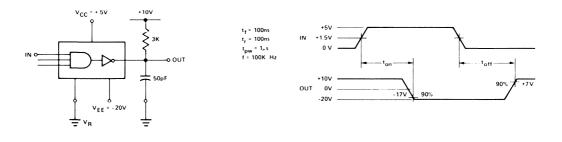

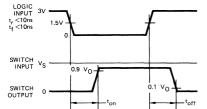

| DG180 2 Channel High-Speed Driver with SPST Junction FET Switches    | ii   | 59       |

| DG181 2 Channel High-Speed Driver with SPST Junction FET Switches    | ii   | 59       |

| DG182 2 Channel High-Speed Driver with SPST Junction FET Switches    | ii   | 59       |

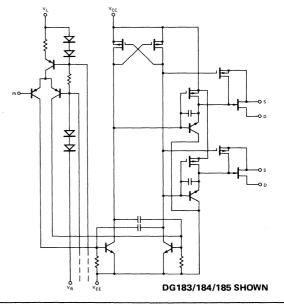

| DG183 2 Channel High-Speed Driver with DPST Junction FET Switches    | ii   | 59       |

| DG184 2 Channel High-Speed Driver with DPST Junction FET Switches    | ii   | 59       |

| DG185 2 Channel High-Speed Driver with DPST Junction FET Switches    | ii   | 59       |

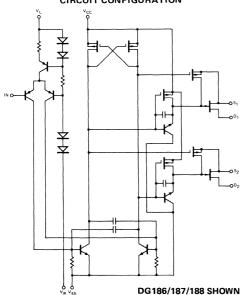

| DG186 1 Channel High-Speed Driver with SPDT Junction FET Switches    | ii   | 59       |

| DG187 1 Channel High-Speed Driver with SPDT Junction FET Switches    | ij   | 59       |

| DG188 1 Channel High-Speed Driver with SPDT Junction FET Switches    | ii   | 59       |

| DG189 2 Channel High-Speed Driver with SPDT Junction FET Switches    | ii   | 59       |

| DG189 2 Channel High-Speed Driver With SPDT Junction FET Switches    | 11   | 59<br>59 |

| DG190 2 Channel High-Speed Driver with SPDT Junction FET Switches    | ii   | 59<br>59 |

| DGIST 2 Channel High-Speed Driver With SPDT Junction FET Switches    | •••  |          |

| G115 6 Channel Enhancement Type MOS FET Switch                       | !    | 154      |

| G116 5 Channel Enhancement Type MOS FET Switch                       | !    | 158      |

| G117 5 Channel Enhancement Type MOS FET Switch                       | 1    | 158      |

| G118 6 Channel Enhancement Type MOS FET Switch                       | !    | 158      |

| G119 6 Channel Enhancement Type MOS FET Switch                       | !    | 158      |

| G123 4 Channel Enhancement Type MOS FET Switch                       |      | 154      |

| G125 4 Channel Junction FET Switch                                   | 1    | 162      |

| G126 4 Channel Junction FET Switch                                   | 1    | 162      |

| G127 4 Channel Junction FET Switch                                   | !    | 162      |

| G128 4 Channel Junction FET Switch                                   | ļ.   | 162      |

| G129 4 Channel Junction FET Switch                                   | 1    | 162      |

| G130 4 Channel Junction FET Switch                                   | ļ.   | 162      |

| G131 4 Channel Junction FET Switch                                   | ı    | 162      |

| A 1 0 11 1 2 2 2 2                                                                                                                 |                                         |        |            |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------|------------|

| Analog Switches, cont. G132 4 Channel Junction FET Switch                                                                          |                                         | Vol.   |            |

| G1330 4 Channel Junction FET Switch                                                                                                |                                         | 1      | 162<br>162 |

| G1340 4 Channel Junction FET Switch                                                                                                |                                         | i      | 162        |

| G1350 4 Channel Junction FET Switch                                                                                                |                                         | i      | 162        |

| G1360 4 Channel Junction FET Switch                                                                                                |                                         | i      | 162        |

| IH181 Low Power equivalent to DG181                                                                                                |                                         | i      | 148        |

| IH182 Low Power equivalent to DG182                                                                                                |                                         | i      | 148        |

| IH184 Low Power equivalent to DG184                                                                                                |                                         | 1      | 148        |

| IH185 Low Power equivalent to DG185                                                                                                |                                         | 1      | 148        |

| IH187 Low Power equivalent to DG187                                                                                                |                                         | 1 ,    | 148        |

| IH188 Low Power equivalent to DG188                                                                                                |                                         | 1      | 148        |

| IH190 Low Power equivalent to DG190                                                                                                |                                         | !      | 148        |

| IH191 Low Power equivalent to DG191IH200 2 Channel SPST CMOS Switch                                                                | • • • • • • • • • •                     | ļ      | 148        |

| IH5001 1 Channel Driver with SPST FET Switches with Gate Available                                                                 |                                         | II .   | 73<br>164  |

| IH5002 1 Channel Driver with SPST FET Switches with Gate Available                                                                 |                                         | i      | 164        |

| IH5003 2 Channel Driver with SPST FET Switches with Gate Available                                                                 | • • • • • • • • • • • • • • • • • • • • | 1      | 166        |

| IH5004 2 Channel Driver with SPST FET Switches with Gate Available                                                                 |                                         | i      | 166        |

| IH5005 2 Channel Driver with SPST FET Switches with Gate Available                                                                 |                                         | i      | 168        |

| IH5006 2 Channel Driver with SPST FET Switches with Gate Available                                                                 |                                         | i '    | 168        |

| IH5007 2 Channel Driver with SPST FET Switches with Gate Available                                                                 |                                         | ı      | 168        |

| IH5009 Low Cost 4 Channel SPST FET Switches with Compensating FET                                                                  |                                         | ı      | 172        |

| IH5010 Low Cost 4 Channel SPDT FET Switches with Compensating FET                                                                  |                                         | ı      | 172        |

| IH5011 Low Cost 4 Channel SPDT FET Switches                                                                                        |                                         | ı      | 172        |

| IH5012 Low Cost 4 Channel SPDT FET Switches                                                                                        |                                         | ŀ      | 172        |

| IH5013 Low Cost 3 Channel SPDT FET Switches with Compensating FETIH5014 Low Cost 3 Channel SPDT FET Switches with Compensating FET | •,•••••                                 | !      | 172        |

| IH5015 Low Cost 3 Channel SPDT FET Switches                                                                                        | • • • • • • • • • • • • • • • • • • • • | l<br>I | 172        |

| IH5016 Low Cost 3 Channel SPDT FET Switches                                                                                        | • • • • • • • • • • • • • • • • • • • • | -      | 172<br>172 |

| IH5017 Low Cost 2 Channel SPDT FET Switches with Compensating FET                                                                  |                                         | i      | 172        |

| IH5018 Low Cost 2 Channel SPDT FET Switches with Compensating FET                                                                  |                                         | i      | 172        |

| IH5019 Low Cost 2 Channel SPDT FET Switches                                                                                        |                                         | i      | 172        |

| IH5020 Low Cost 2 Channel SPDT FET Switches                                                                                        |                                         | 1      | 172        |

| IH5021 Low Cost 1 Channel SPDT FET Switches with Compensating FET                                                                  |                                         | 1      | 172        |

| IH5022 Low Cost 1 Channel SPDT FET Switches with Compensating FET                                                                  |                                         |        | 172        |

| IH5023 Low Cost 1 Channel SPDT FET Switches                                                                                        |                                         | !      | 172        |

| IH5024 Low Cost 1 Channel SPDT FET Switches IH5025 Low Cost 4 Channel SPST FET Switches                                            |                                         | !      | 172        |

| IH5026 Low Cost 4 Channel SPST FET Switches                                                                                        | • • • • • • • • • • • • • • • • • • • • | !      | 178        |

| IH5027 Low Cost 4 Channel SPST FET Switches                                                                                        |                                         | -      | 178<br>178 |

| IH5028 Low Cost 4 Channel SPST FET Switches                                                                                        |                                         | i      | 178        |

| IH5029 Low Cost 3 Channel SPST FET Switches                                                                                        |                                         | i      | 178        |

| IH5030 Low Cost 3 Channel SPST FET Switches                                                                                        |                                         | ĺ      | 178        |

| IH5031 Low Cost 3 Channel SPST FET Switches                                                                                        |                                         | 1      | 178        |

| IH5032 Low Cost 3 Channel SPST FET Switches                                                                                        |                                         | 1      | 178        |

| IH5033 Low Cost 2 Channel SPST FET Switches                                                                                        |                                         | 1      | 178        |

| IH5034 Low Cost 2 Channel SPST FET Switches                                                                                        |                                         | 1      | 178        |

| IH5035 Low Cost 2 Channel SPST FET Switches IH5036 Low Cost 2 Channel SPST FET Switches                                            |                                         | . !    | 178        |

| IH5037 Low Cost 1 Channel SPST FET Switches                                                                                        | • • • • • • • •                         |        | 178        |

| IH5038 Low Cost 1 Channel SPST FET Switches                                                                                        |                                         | 1      | 178<br>178 |

| IH5040 High Level 1 Channel CMOS Monolithic SPST Switch                                                                            |                                         | i      | 184        |

| IH5041 High Level 2 Channel CMOS Monolithic SPST Switch                                                                            | • • • • • • • • • •                     | i      | 184        |

| IH5042 High Level 1 Channel CMOS Monolithic SPDT Switch                                                                            |                                         | i      | 184        |

| IH5043 High Level 2 Channel CMOS Monolithic SPDT Switch                                                                            |                                         | 1      | 184        |

| IH5044 High Level 1 Channel CMOS Monolithic DPST Switch                                                                            |                                         | 1      | 184        |

| IH5045 High Level 2 Channel CMOS Monolithic DPST Switch                                                                            |                                         | 1, 1,  | 184        |

| IH5046 High Level 1 Channel CMOS Monolithic DPDT Switch                                                                            |                                         | ļ      | 184        |

| IH5047 High Level 1 Channel CMOS Monolithic 4PST Switch                                                                            |                                         | 1      | 184        |

| IH5048 High Level 2 Channel SPST CMOS Switch IH5049 High Level 2 Channel DPST CMOS Switch                                          | • • • • • • • • • • • • • • • • • • • • | 1      | 184        |

| IH5050 High Level 1 Channel SPDT CMOS Switch                                                                                       | • • • • • • • • • •                     | I s    | 184        |

| IH5051 High Level 2 Channel SPDT CMOS Switch                                                                                       | • • • • • • • • •                       |        | 184<br>184 |

| IH5060 16 Channel CMOS Analog Multiplexer                                                                                          |                                         | i      | 198        |

| IH5070 8 Channel Differential CMOS Analog Multiplexer                                                                              |                                         | i i    | 204        |

|                                                                                                                                    |                                         |        | •          |

| - |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|--|

|   | Analog Switches, cont.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Vol.  | Page             |  |

|   | MM450/MM550 2 Channel-Differential Enhancement Type PMOS FET Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 1   | 210              |  |

|   | MM451/MM551 4 Channel Enhancement Type PMOS FÉT Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | i     | 210              |  |

|   | MM452/MM552 4 Channel Enhancement Type PMOS FET Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | i     | 210              |  |

|   | MM455/MM555 3 Channel Enhancement Type PMOS FET Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | i     | 210              |  |

|   | Will to Million of Chamber Emandement (ppe 1 Mee 1 E 1 extent)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •     | 2.10             |  |

|   | Analog Switch Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                  |  |

|   | D112 2 Channel FET Switch Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1     | 120              |  |

|   | D113 2 Channel FET Switch Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i     | 120              |  |

|   | D120 2 Channel FET Switch Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i     | 120              |  |

|   | D121 2 Channel FET Switch Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i     | 120              |  |

|   | D123 6 Channel FET Switch Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 1   | 124              |  |

|   | D125 6 Channel FET Switch Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1     | 124              |  |

|   | D129 4 Channel MOS FET Switch Driver with Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · ii  | 57               |  |

|   | Di29 4 Chainel MOS FET Switch Driver with Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "     | 57               |  |

|   | Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                  |  |

|   | 111 Precision Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ١     | 24               |  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 1   |                  |  |

|   | 211 Precision Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | !     | 24               |  |

|   | 311 Precision Voltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - !   | 24               |  |

|   | 8001 Precision Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 66               |  |

|   | LM139 Quad Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | !     | 32               |  |

|   | LM139A Quad Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ı     | 32               |  |

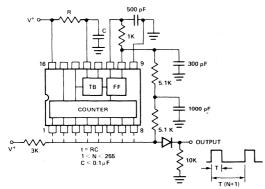

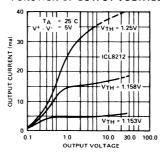

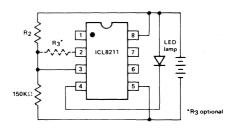

|   | LM239 Quad Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 1   | 32               |  |